Cadence Spetre

Cadence spectre是cadence针对全日制集成电路推出的仿真工具,主要用于模拟及数模混合集成电路的仿真,用在linux系统工作站中。

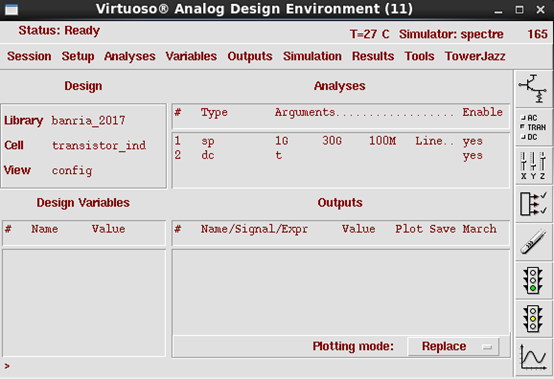

Cadence ADE仿真环境

ADE:Analog Design Environment

新建文件

新建原理图:

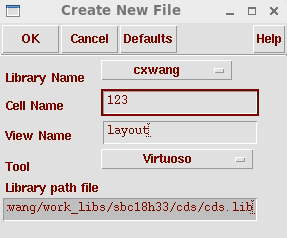

新建版图

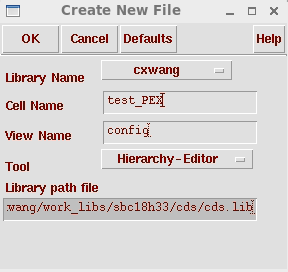

新建config文件:(用来连接原文件与test文件的文件,可以在test schematic文件中调用原文件生成的寄生文件calibre)

Layout常用快捷键

缩小界面

o:reduce the interface

shift+z:reduce the interface

缩小界面,与o的作用相同

放大界面

右键选中:enlarge the interface

放大界面。将需要放大的区域点击右键选中,即可将该区域放大。

居中

f:centered

显示单元器件

shift+f

隐藏单元器件

Ctrl+f

复制

C:copy

可选择其中一个元器件复制,也可以先选中一个区域进行复制。在同一文件和跨文件都可使用。

粘贴

V:paste

调用元件

I:Instance

查看器件属性

q:quality

退出当前快捷操作

Esc

拉伸

s:stretch

使用时不能选中任何器件,点击s,将鼠标放到需要拉伸的一边,这时这一边可闪烁变成虚线,点击该边,向需要拉伸的一边拖拽即可。

拉伸矩形框时直接拉伸任意一边即可,但拉伸路径时,需要拉伸路径的中心线。

画矩形

r :rectangle

点击r,可在选中的任意一层画矩形。

尺子

k:ruler

点击k,可画尺子。注意:尺子一旦画好之后便不能修改尺寸,因此,若想使用精确尺度,就需要在放尺子的时候直接确定好尺寸,可通过放大缩小界面来实现。

注意:画尺子时,可以配合F3使用,用来改变尺子的角度。(diagonal:45°,orthogonal:90°,horizontal:水平方向,vertical:垂直方向,anyAngle:任意角度)

删除所有尺子

shift+k:

画路径

P:path

与ADS中的路径使用方法相似,但在拐弯处不能选择弯折的角度,若需要45°脚弯折,则需要手动画一段45°斜角的线。

也可以配合F3键使用,来改变路径的宽度。

上下翻转

b

左右翻转

shift+b

移动

m:move

但只能上下左右移动,若在OptionàDisplayàSnap Modesàdiagonal设置了,则可以向45°斜角方向进行移动。

旋转

Editàotheràrotate

旋转。选中需要旋转的单元,像画尺子一样选择一个方向,即可向该方向旋转。

注意:为了精确地画每根线,需要在画之前摆放尺子。

Schemtic常用快捷键

调用元件

I:instance

查看属性

Q:quality

复制

C:copy

可选择其中一个元器件复制,也可以先选中一个区域进行复制。在同一文件和跨文件都可使用。

粘贴

V:paste

居中

f:centered

退出当前快捷操作

Esc

连线

W:wire

放大缩小

可滚动滑轮直接对界面进行放大和缩小。

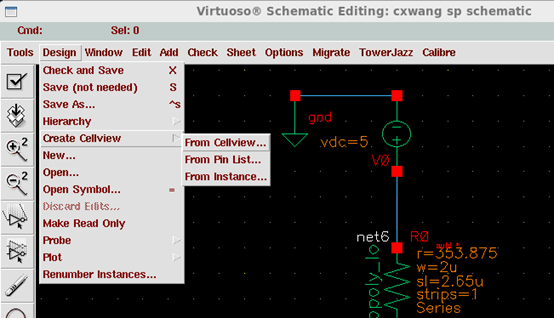

Symbol的制作

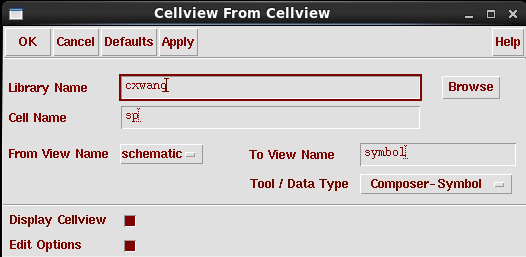

在绘制好的原理图界面,点击DesignàCreat CellviewàFrom Cellview,如下图:

出现下图:

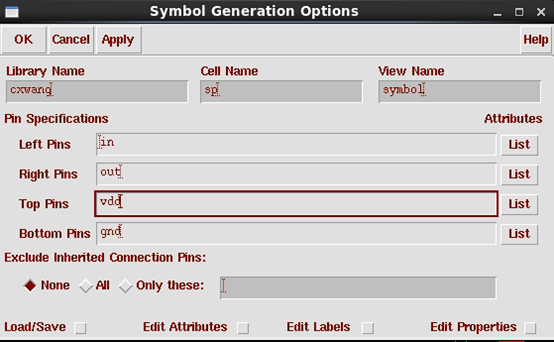

点击OK,出现下图

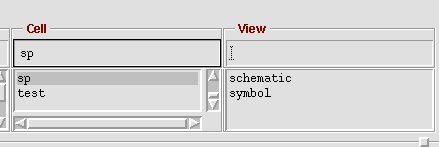

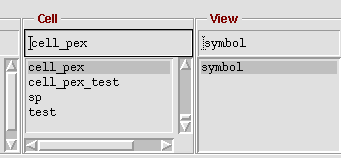

此时,可以修改symbol中各个端口的位置,修改之后点击OK即可在Library manager该Cell文件的View目录下多了一个symbol文件,如下图。

Cadence中自动生成版图文件

该功能与ADS中PCB或MMIC自动生成版图的功能相同,不需要再在版图中一个元件一个元件重新调用,避免了两个文件中调用元件不同导致后面lvs出现元件不匹配错误的问题。

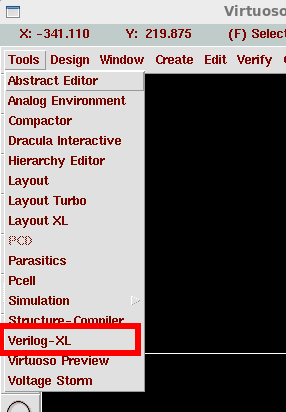

在新建的版图文件中,选择ToolàLayout XL(注意:前提是新建的版图文件需要与原理图文件名称保持相同,或者需要直接在原理图所在的Cell文件中新建layout文件)

可能没有显示明显的变化,但实质上是有变化的。

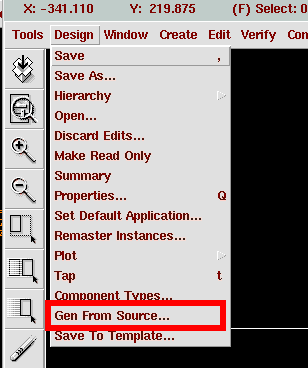

点击DesignàGen From Source

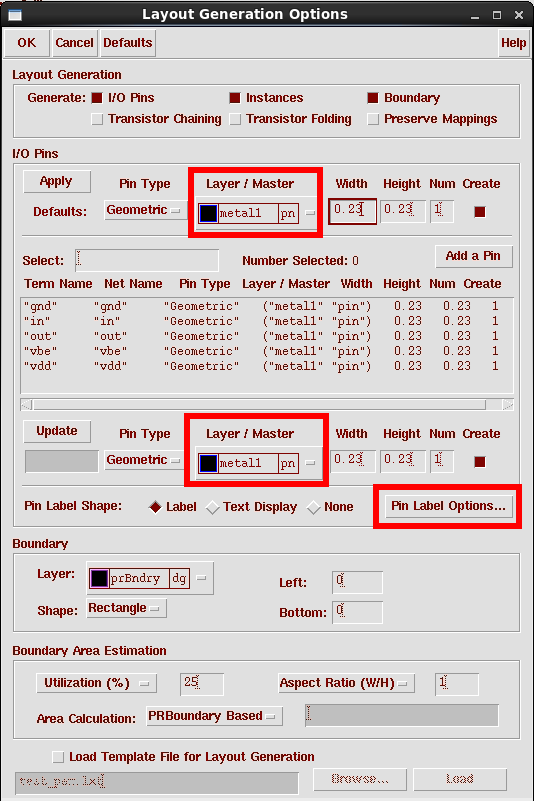

得到下图:

注意:需要在I/Opins 栏中,将NWELLpn改为METAL1pn,主要不要改错

了,不是METAL1dg,然后点击Apply,可以发现中间的4个端口参数都变了。另外在Pin LabelShape栏中,选中Lable,点击后面的PinLabelOptions,打开下面对话框

可以对Pin Lable根据实际需要进行大小的设置。

然后生成的文件中就会包含原理图中对应的器件以及pin Lable,最后根据实际需要摆放的器件位置进行调整,并进行连线。

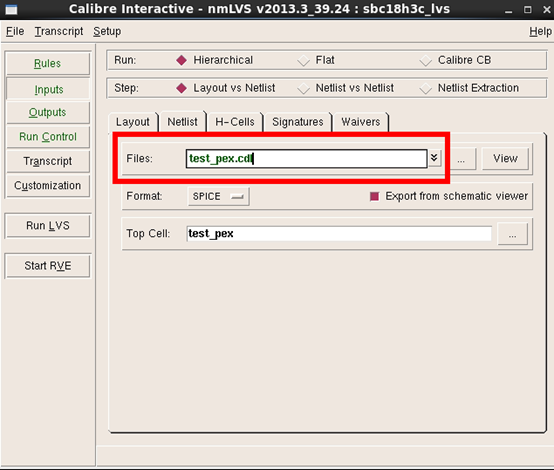

Lvs操作流程:

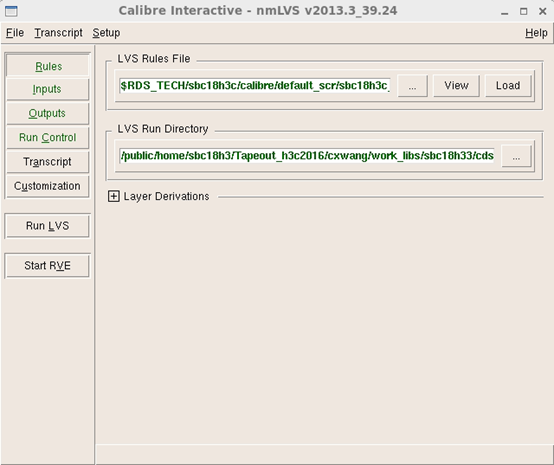

在版图文件中,选择CalibreàRun LVS,出现下面的界面:

装载rulesfile ,选择lvs目录,强烈建议在那建好的cell文件目录下新建一个lvs目录,它

将生成很多文件,也不要用drc目录。

可以点开每一个控键看看里面有什么,如果没有显示红色,则证明文件正常,选择默认即可。如果文件显示红色,则需要注意是否有异常,这样可能直接导到lvs无法仿真。

然后根据仿真的结果一个一个排查原因

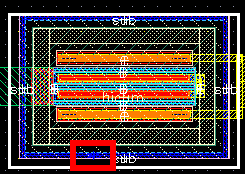

过lvs时,版图中必须有"sub"Lable,可以直接在版图中添加"sub"标签。

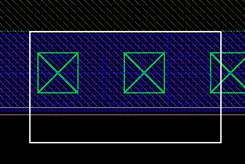

如晶体管的sub可以这样标注:

放大之后可以看到:

其中Lable的层选择为Metal1 pn层,而不是Metal1 dg层。

遇到的问题:

Netlist中的.cdl文件显示红色,这里图中只表示对应位置,没有记录实际显示红色的情况。

再看CIW中的提示:

$Error: loadcontext:could not open file -"/eda/cadence/ic5141/tools.lnx86/dfii/etc/context/64bit/aucore.cxt"

查找问题是:该程序运行时需要32位操作系统的支持,而所用系统为64位系统,发生了冲突,已与负责软件安装的同学进行联系,并解决了问题。

Cadence后仿操作

Cadence后仿操作必须先过lvs,如果lvs出现了问题,在进行后仿的时候问题会同时发生。

2.1 PEX参数提取(有些地方也叫XRC仿真)

通常Calibre PEX先执行LVS,之后提取寄生参数,最后将原有的器件和提取出的寄生电容电阻电感等反馈到一个带寄生信息的电路图中。

过lvs

步骤与上述过lvs的步骤相同。

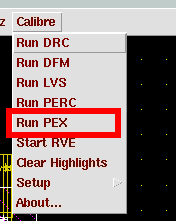

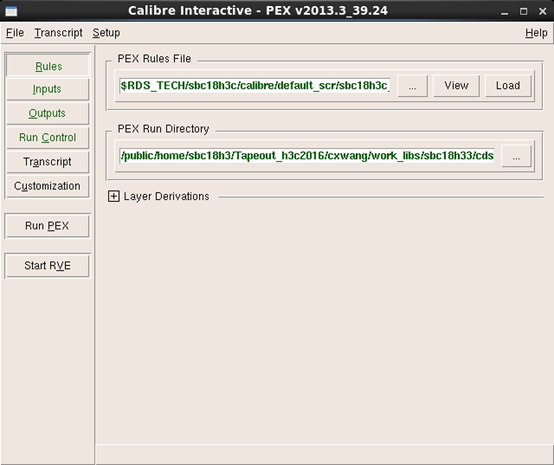

在layout文件中选择CalibreàRun PEX

会出现如图所示的对话框:

这里的文件所在目录可以选择与lvs相同的目录,两个中的部分文件可以共享。

同样,如果没有显示红色的地方,都可以采用默认。

注意:

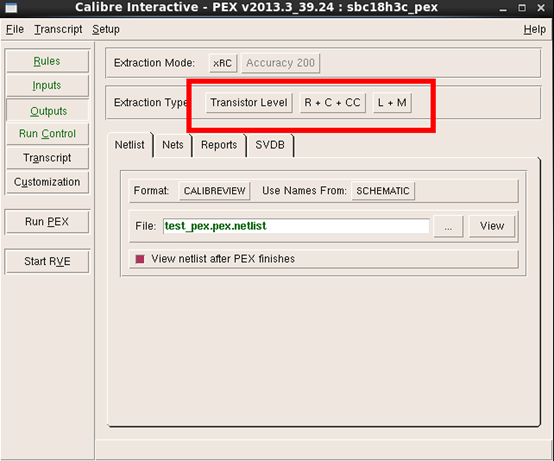

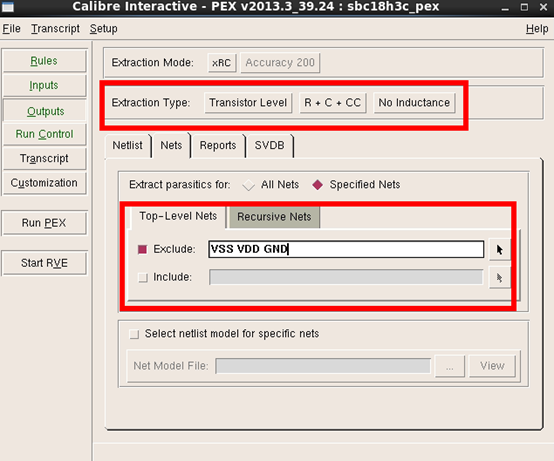

在Outputs选项框里,可以选择Extraxtion Type。根据实际仿真电路,可以选择所提取的参数的电容、电阻、电感、互容、互感、晶体管等效应,以使所提取的寄生模型更接近实际情况。

Extraction Type里面,第一项为了得到最精确的提取,通常选择Transistor Level,代表晶体管级的提取。第二项R代表寄生电容,C代表本征寄生电容(对地节点的电容),CC代表耦合电容。第三项L代表寄生电感,M代表互感。

仿真之后,就会弹出该对话框:

和

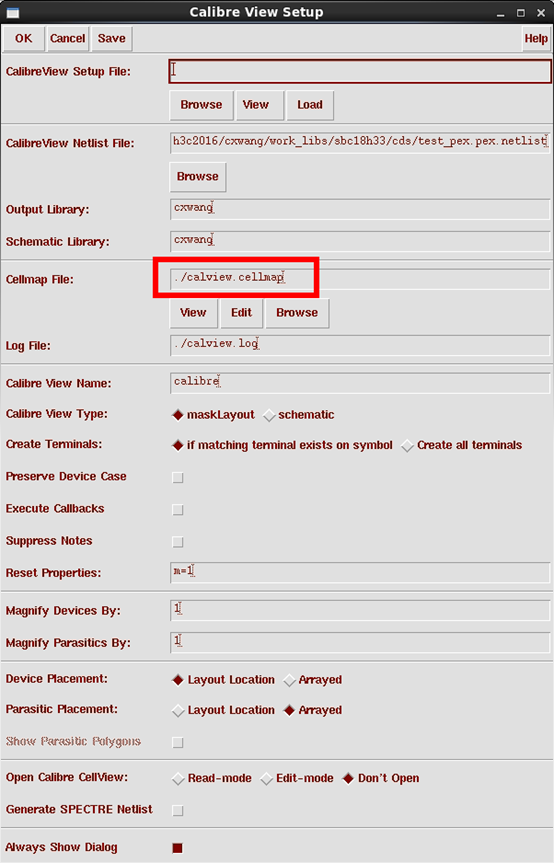

这里关键是要输入Cellmapfile的路径,然后在CalibreViewName里面输入要生成的名字,这里输入calibre就可以。

点击ok。

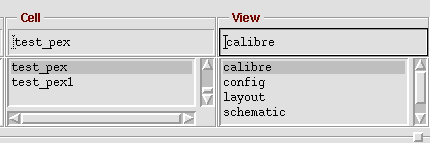

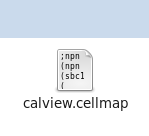

如果没有异常就会在LibraryManager里面看到多了个View: calibre

这样,版图提取就完成了,版图提取后的文件就是calibre。

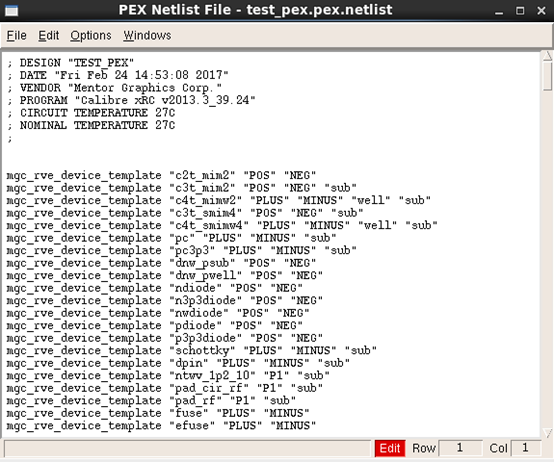

双击View中的calibre就可以看到:

这些就是提取出来的寄生参数,同时也包含所提取器件的参数,可以通过放大文件看到。

接下来就是后仿,要生成用于后仿的文件。

遇到的问题:

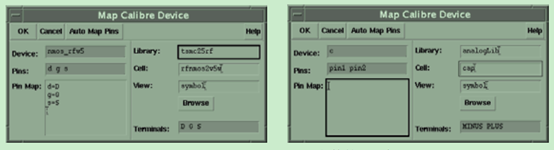

calview.cellmap文件是用来建立原理图和版图器件映射关系的一个文件,但是这里默认的calview.cellmap文件并不能建立这个关系。在上面的Calibre Setup View界面设置之后点击OK,会弹出对话框:

该文件提示需要手动建立map配置。虽然在PEX Netlist File文件中弹出了关于对应配置关系的代码,但是看不懂。而且如此众多的器件若都进行手动设置的话显然不可能。况且,Map Calibre Device提示栏中Pins栏中的数目与Terminals的数目并不相同,无法进行手动配置。

解决方法:

calview.cellmap文件本是工艺库Foundry可以直接提供的,而且在仿真PEX时首页面Rules中直接调用的就是Foundry提供的rules,可能只是默认的calview.cellmap文件配置不上我们想调用的文件。所以想起在电脑中直接搜索有没有其他的calview.cellmap文件。发现确实有:

把这个文件复制到我们的文件目录下,再在Calibre Setup View界面重新选择calview.cellmap。这时发现Map Calibre Device不见了。

新建symbol

与上述建立symbol的方法相同

新建test文件

Test文件在建立时需要与原文件建立在不同的cell文件下,是上层文件。如图所示:

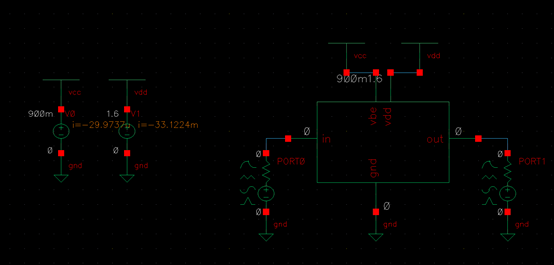

需要先调用原文件中的symbol,然后在symbol的每个端口连接外围电路。如图所示:

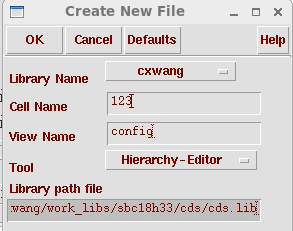

新建Config文件

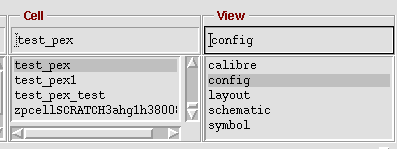

在原理图和版图所在Cell文件中新建config文件。

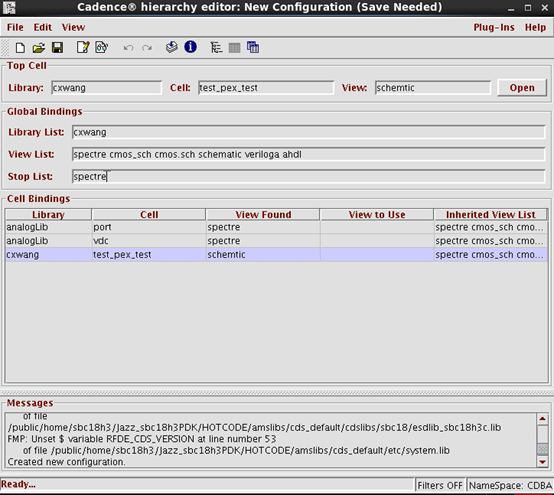

注意上图中, Cell name还是要在 sche中, Tool改为 Hierarchy-Editor, ViewName就会自动变为 config。点击 Ok。可以看到多了个文件:

同时出来两个窗口

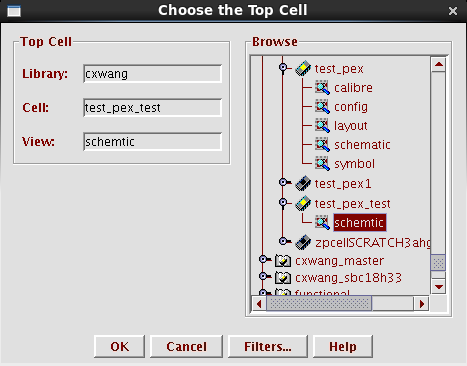

点击左边的窗口的 Browse...将出现下面窗口。

选择test文件中的schemtic,这时不要选原文件中的schemtic,因为顶层文件是test文件,需要在test文件中调用其它文件。

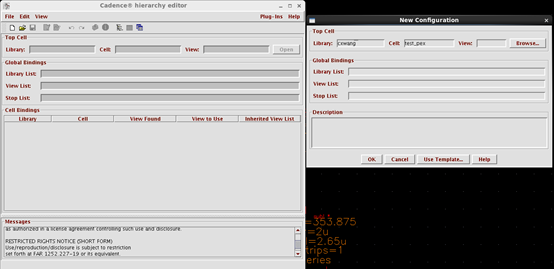

然后点击 中的use template,得到:

中的use template,得到:

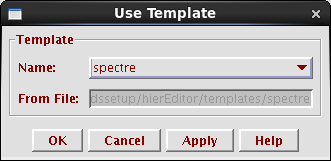

Name选择spectre,点击OK

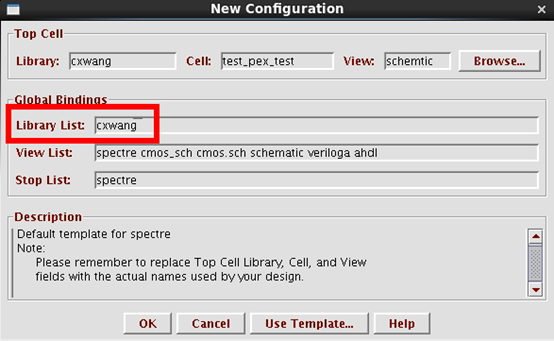

在该框中Library List选择与Top Cell中Library相同的Library。点击OK,出现:

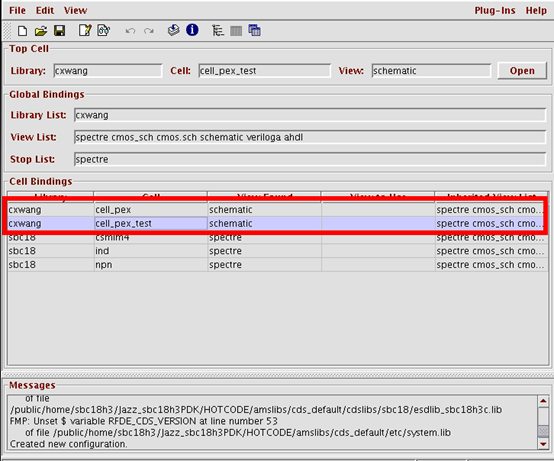

需要明确我们这一步的意图是想在test文件中调用原理图和版图中的文件,上面的步骤已经将版图中提取的寄生参数生成之后保存成了calibre文件,这里就是想用config这样一个中转站将calibre调用到test文件中。所以这里的Cell Bindings需要将calibre所在的原Cell文件的View改成calibre以备调用。

遇到的问题:

如上图所示,Cell Bindings所列Cell文件中只有test文件而没有原文件,无法进行设置和修改。如上图所示。

而该界面本该是这样的:

即原文件和测试文件都包含

解决方法:

尝试了打开新建的config文件和test文件,发现这两个文件中的东西是一样的。

Config文件的用途:

就是将原文件与测试文件联系起来,因为测试文件中可以调用原文件中的symbol,而且可以加外围测试电路,而config文件中的东西与测试文件中的相同。

发现问题在于:

测试文件中没有调用原文件中的symbol,是空文件,因此config文件无法将两个文件联系起来。

也就是需要在新建config文件之前需要将测试文件中的测试电路搭建好,并且里面必须包含原文件的symbol,这样才能真正将这个映射关系建立起来。

然后才能进行下一步

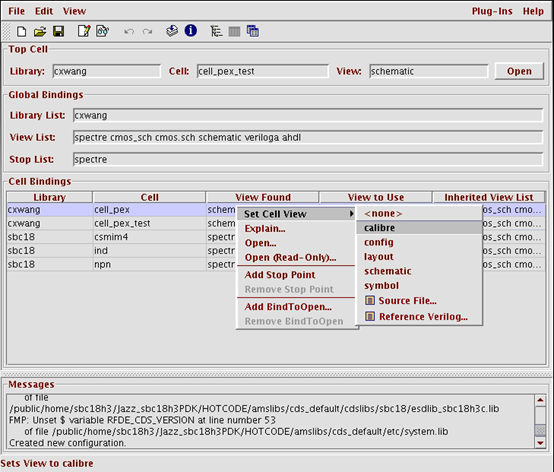

将原文件的View to Use改成Calibre,并保存。

当然这里也可以选择schemtic。也就是可以实现和ADS中一样的功能:该模块如果调用的是原理图,那么所仿真的结果就是原理图的仿真结果;如果调用的是Calibre文件,那么所仿真的结果就是提取寄生参数之后的仿真结果。

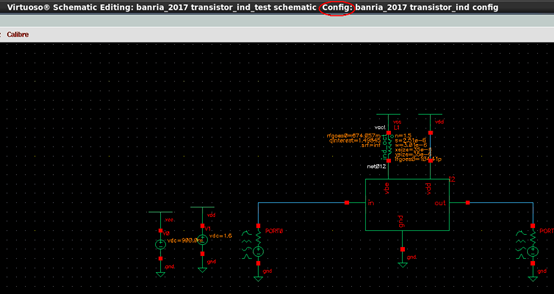

在calibre文件中进行后仿真

注意:测试结果的仿真必须在Calibre文件中仿真,而不是在test文件中仿真,因为test文件无法调用原文件提取寄生参数之后的Calibre文件。

点击e可以进入symbol内部,ctrl+e则返回该界面。

示例

以一个只有电容的无源电路为例。

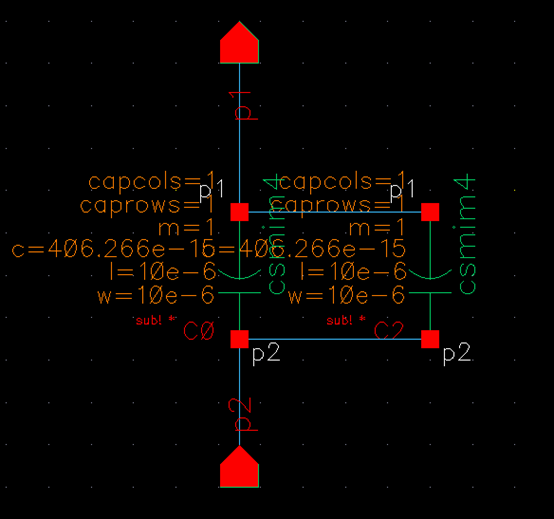

原理图为:

因为过lvs时要求电路中必须有回路,所以建立了两个电容并联的电路。

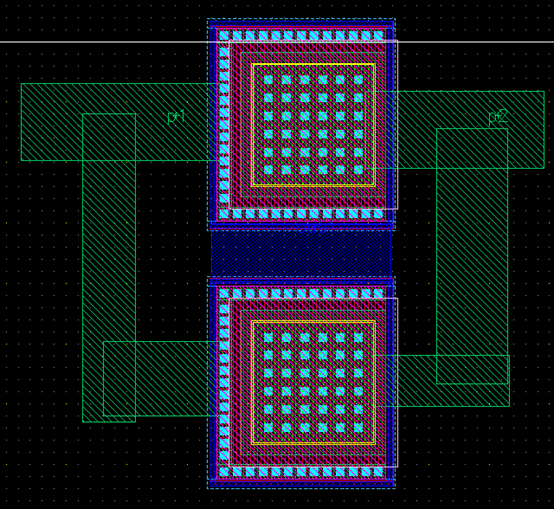

版图为:

因为lvs要求版图文件中必须有sub,所以就将电容中的sub都显示了出来,并且将两个电容的sub连接在一起,并打上Lable。

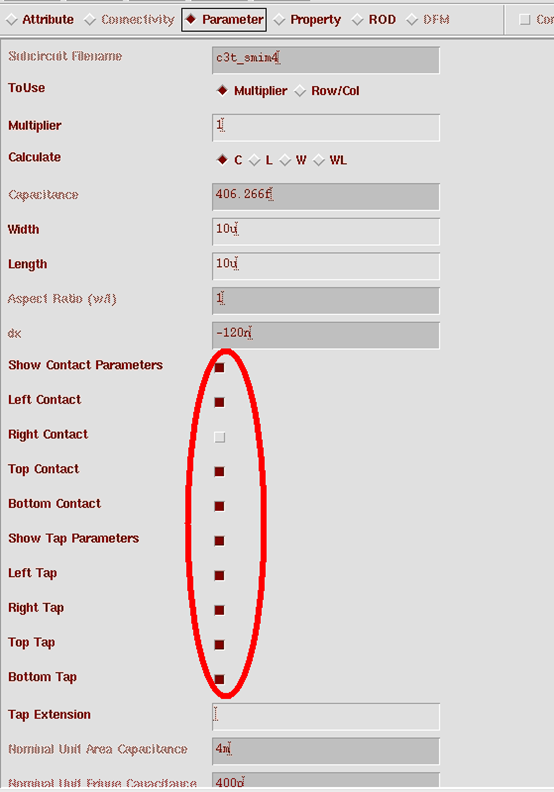

(可以选择都勾上,原理图中勾不勾都行)

仿真PEX提取寄生参数时,注意在outputs界面的仿真设置:

因为该电路中没有电源和地,也没有电感,所以需要都去掉,否则仿真会报错。

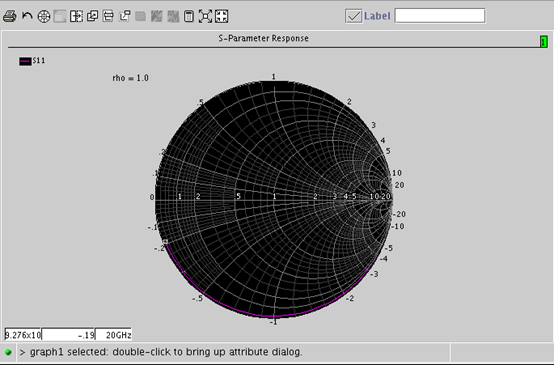

按照上面的步骤进行,得到仿真的原理图的结果是:

原理图仿真的电容实部是:9.276*10-3,虚部是-1.9

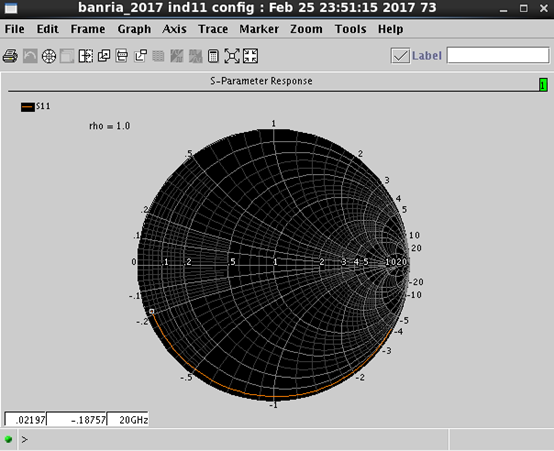

提取寄生参数之后,Calibre文件仿真电容的实部是0.02197,虚部是-1.8757.

可见,提取寄生参数之后,实部变大,符合实际情况,证明参数的提取方法使正确的。

网友留言: