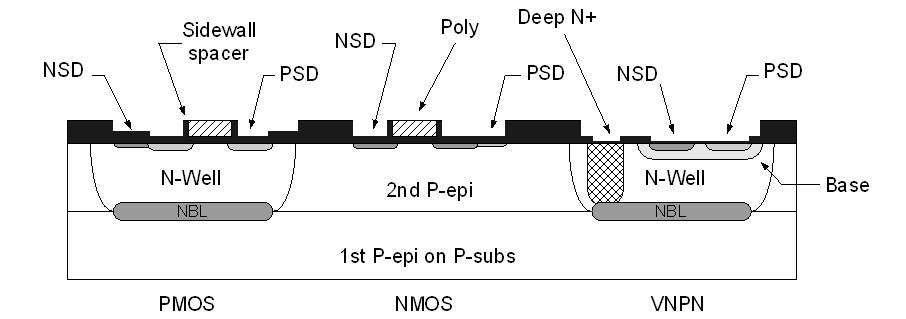

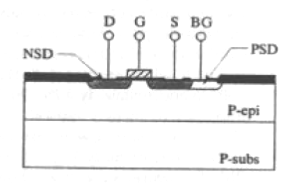

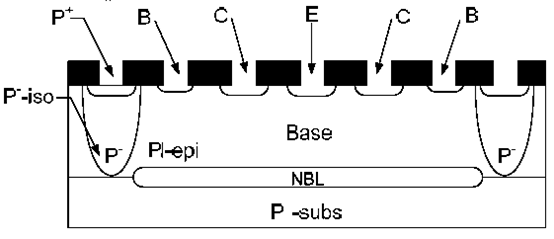

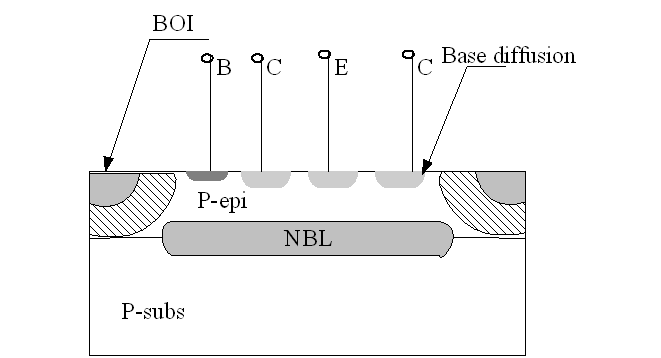

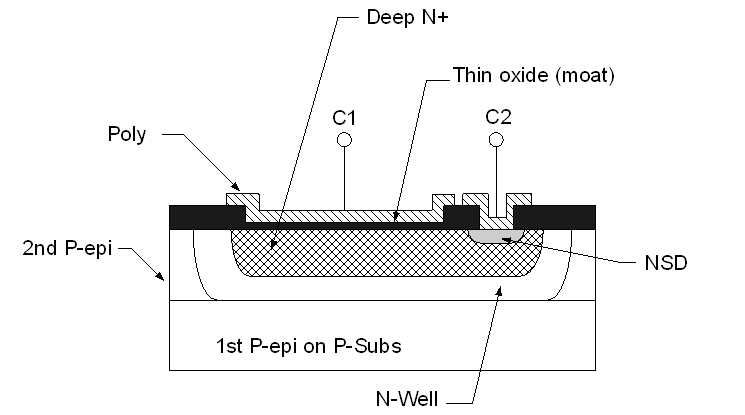

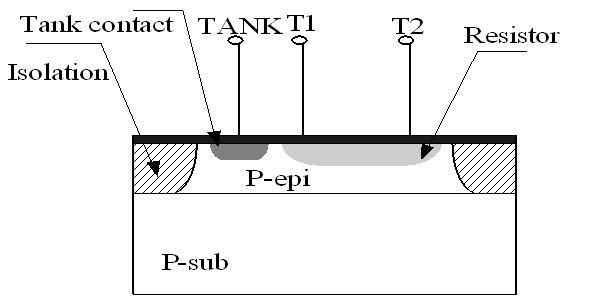

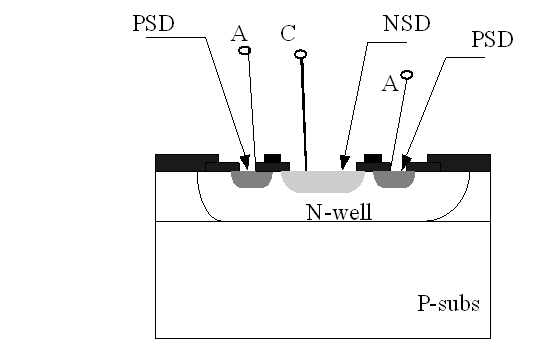

采用1.2um的Analog BiCMOS工艺,两层金属互连线、一层多晶硅,即1P2M的BiCMOS,电路结构为数模混合的BiCMOS硅栅结构。P衬底P外延,N阱,集电极扩散隔离(CDI, collector-diffused-isolation)。其典型工艺剖面图如下:其图如下:

图1 在Metallization and Protective Overcoat工序之前的BiCMOS典型工艺剖面图

- MOS Transistor

版图上出现的MOS管大部分都是典型的工艺,对于典型工艺的MOS,我们只给出Poly层照片及其Cross section,不做特别说明。

1、PMOS

图2 PMOS Transistor的Poly层照片

图3 Cross section of a PMOS Transistor

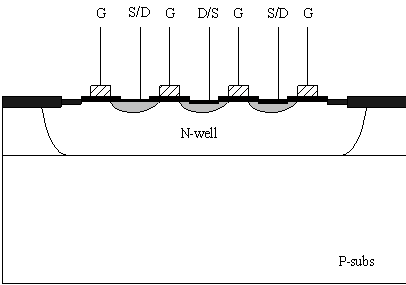

2、nmos

图4 NMOS Transistor的Poly层照片

图5 Cross section of a NMOS Transistor

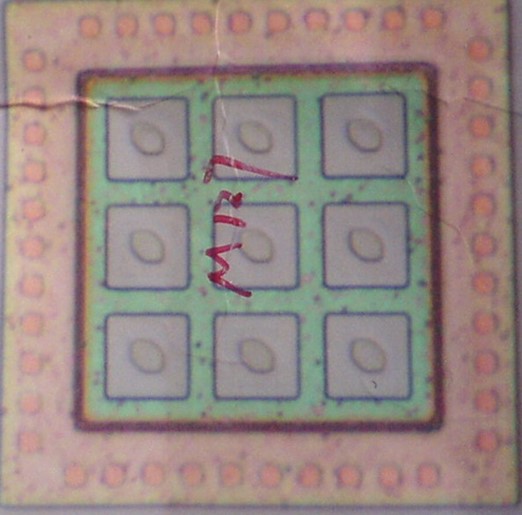

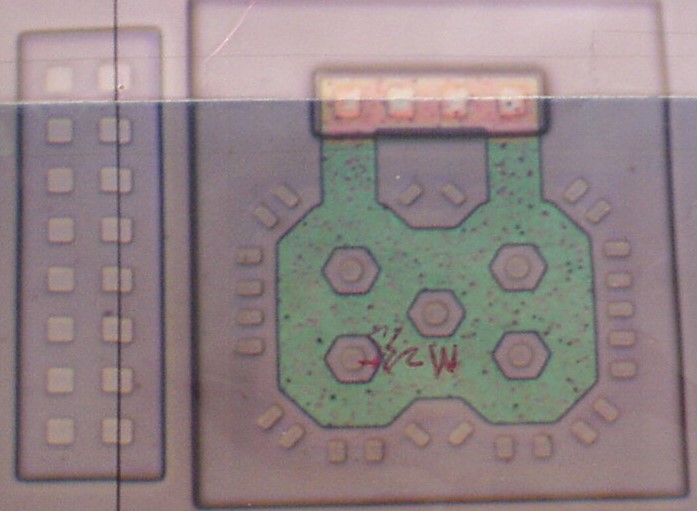

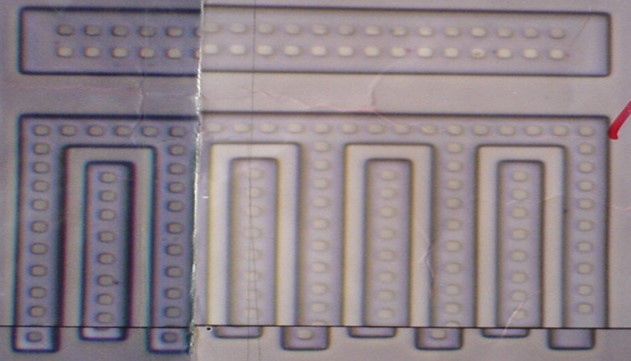

3、Waffle transistor

版图上的一半面积都用来做电路中的一个关键器件——Waffle transistor,版图示意如上。源漏区域为矩阵结构,且漏极也做在n阱中,为非自对准工艺,可承受高压大电流。Waffle transistor比常规的交叉指型管多提供33%的跨导,但是,这将使镀金电阻成为Rds(on)的主要组成部分,而且会使得源漏部分的雪崩击穿电压比晶体管其它部分低,衬底接触也不好。

图6 Waffle Transistor的Poly层照片

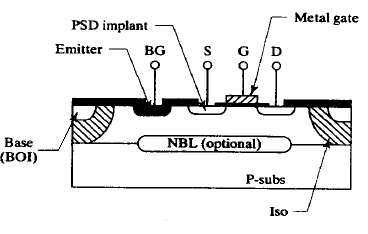

图7 Cross section of a Waffle Transistor

4、VDMOS

图8

二、Bipolar Transistors

版图上出现的BTJ大部分都是典型的Bipolar工艺,对于典型工艺的BTJ,我们只给出Poly层照片及其Cross section,也不做特别说明。

1、PNP transistors

(1)Lateral PNP transistor:

图9Lateral PNP transistor的Poly层照片

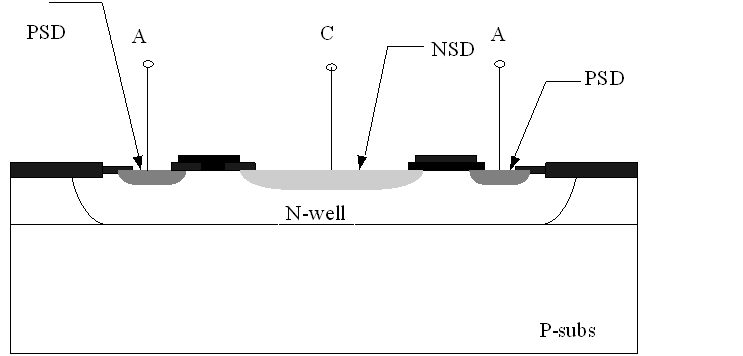

图10 Cross section of a Lateral PNP transistor

(2)Substrate PNP transistor:

图11 Cross section of a Substrate PNP transistor

(3)Split Collector PNP transistor

多集电极晶体管通常用来做成电流镜,一个简单的1:1的电流镜用一个多集电极晶体管的两对集电极构成,这样做可以节省空间,但有可能不如两个单独的横向PNP晶体管精确。

图12Split Collector PNP transistor的Poly层照片

图13 Cross section of a Split Collector PNP transistor

2、NPN transistor:

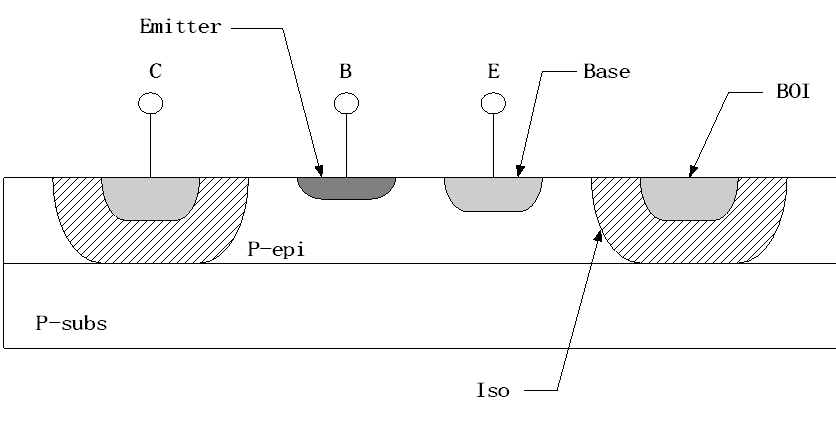

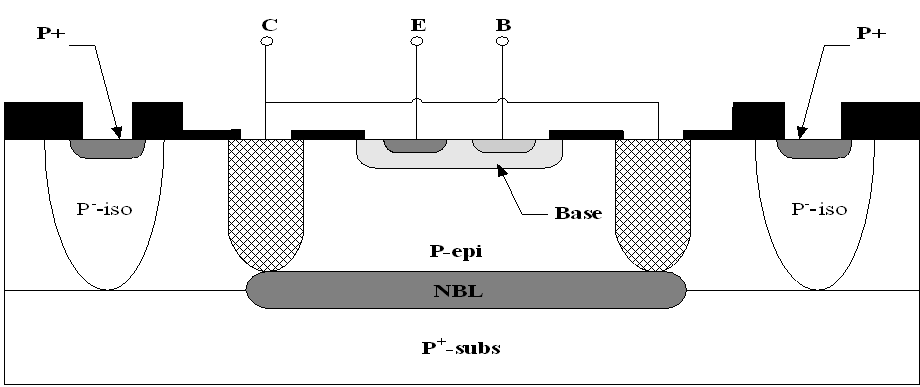

Vertical NPN transistor

图14 Vertical NPN transistor的Poly层照片

图15 Cross section of a Vertical NPN transistor

三、capacitor:

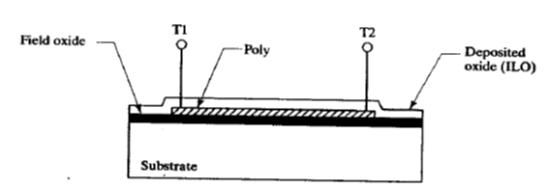

Mos capacitor

图16Mos capacitor的Poly层照片

图17 Cross section of a Mos capacitor

四、resistor

(1)Polysilicon resistor

多晶硅电阻是利用NSD mask进行低掺杂的,根据掺杂浓度不同,其方阻可在几百到几千Ω/口范围内变化。根据器件层颜色判断,LM2716版图上的各个多晶硅电阻的方阻值应是一样的。

多晶硅电阻可以提高电阻值的精度,同时也可以改善相同结构之间的匹配。而且多晶硅电阻对衬底的电容一般比其他类型的电阻对衬底的电容小得多。特别是当电阻较长的时候,具有非常好的线性特性。

图18 Polysilicon resistor的Poly层照片

图19 Cross section of a Polysilicon resistor

2、P Diffused resistor

图20 P Diffused resistor的Poly层照片

图21 Cross section of a P Diffused resistor

五、diode

(1)

图22的Poly层照片

图23

(2)

图24

图25

Reference

黑斯廷斯(Hasting, A)著 《模拟电路版图的艺术》(The Art of Analog Layout)

以上内容来自网络,如有侵权,请联系!

网友留言: