IC 设计流程是每个 IC 从业者的必修课,虽然多数人的从业方向只是 IC 设计流程中的一部分,但是了解 IC 设计流程全貌对正确认识每个 IC 设计环节的作用是有很大帮助的。

对于一个 CAD 来说,了解 IC 设计流程以及每个环节所用 EDA 工具,了解全流程中设计效率的洼地所在,并据此提出系统的解决方案,是整体上提升 IC 设计效率的根本所在,所以同样具有重要意义。

作为一个初入门者的学习笔记,本文多处文本和附图来源于网络,在此不一一注明,感谢原作者。由于本人才疏学浅,有理解错误或描述谬误的地方,请专家批评指正,不胜感激。另外,如非单独指出,本文中的 “IC 设计流程” 均为 “数字设计流程”。

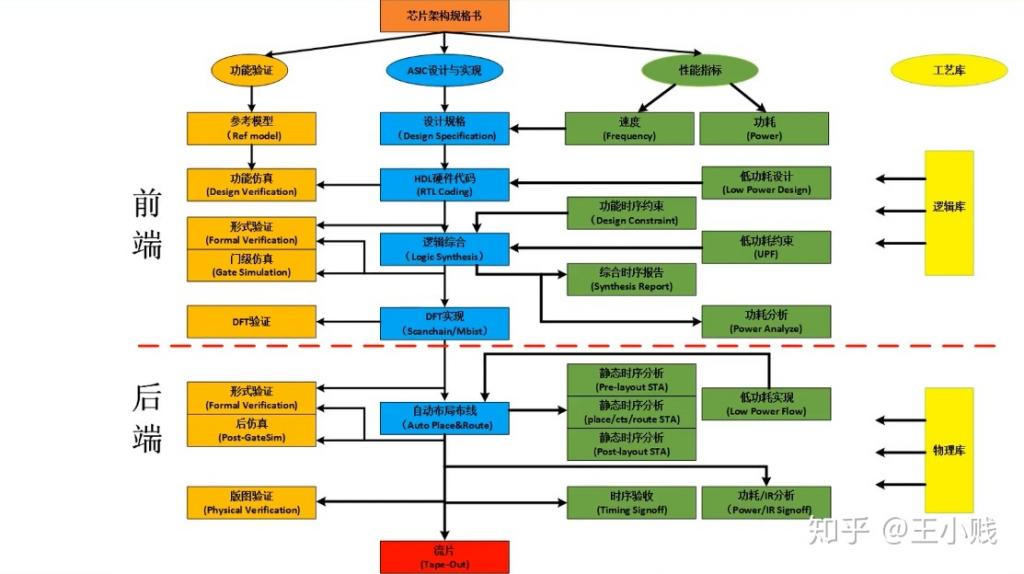

下图是一个 IC 设计全流程的架构图,它的主线是 “ASIC 设计与实现”,为实现这一目的,在考虑到诸如速度和功耗等等 “性能指标” 的前提下,在各个设计环节实现的同时做好 “功能验证” 工作,以保证所有设计环节的 quality。

图一 IC 设计全流程

从逻辑实现还是物理实现这两部分来看,IC 设计流程可以笼统地分为前端和后端两部分。不同的公司有不同差别细微的区分方法,从比较全面的角度来看,我们可以把 IC 设计的完整流程区分为如下几部分。

确定项目需求

一般由项目 PM 来完成,先做市场调研以确定项目需求,对系统功能和能效参数给出指导意见。

系统架构设计

一般由系统架构师完成,确定系统功能细节,定义频率、功耗等参数指标,做顶层的系统仿真模拟,以确定一个可行的芯片设计方案。

前端设计

前端设计(front-end)一般包括 RTL 代码实现和功能仿真。

中端设计

中端设计(mid-end)一般囊括了从功能仿真到物理实现中间所有的环节,包括综合(synthesis),形式验证(formal verification),低功耗设计(low power design),可测试性设计(design for test),STA 等。

简单起见,很多公司也把中端设计归到前端设计的范畴里面。

后端设计

后端设计(back-end)包括布局布线,形式验证,后仿真等。

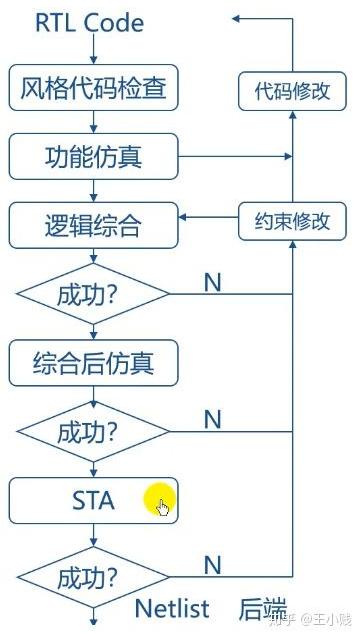

其中,前端和中端的设计流程如下所示。前端从编写 RTL 代码开始,中端的最终交付产品为 netlist。

图二 前端和中端设计流程

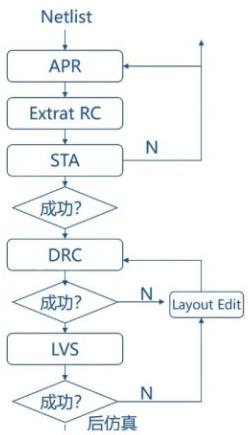

后端的设计流程如下所示。后端的输入为 netlist,最终输出为 GDSII 格式的文件,交由芯片制造商流片。

图三 后端设计流程

那么在不同的 IC 设计流程,各家 EDA 厂商有哪些主流的 EDA 工具来辅助设计实现呢?

表一 IC 设计流程对应的 EDA 工具

IC 流程 | Cadence | Synopsys | Mentor | Others |

模拟仿真与版图 | Virtuoso | |||

RTL 仿真 | VCS | ModelSim | ||

综合 | Genus | Dc | ||

形式验证 | Formality | |||

Spice 仿真 | Spectre | Hspice | ||

时序 | Tempus | Pt | ||

DFT | DFTCompiler | Tessent | ||

布局布线 | Encounter/Innovus | ICC/ICC2 | ||

物理验证 | PVS | Calibre | ||

寄生参数提取 | Quantus | Star-RCXT | Calibre-XACT | |

k 库 | Liberate | Silicon-smart |

有一些 EDA 工具经历过一些大的版本迭代和合并升级,名字会有所不同,有不准确的地方请指正。

之所以给 cadence 列出这么多产品,并不是说它的 EDA 工具在每个流程环节都占有主要的市场地位,主要是说明它有比较全的全流程工具链,其中 Virtuoso 具有绝对的市场地位,Innovus 和 Liberate 具有领先的市场地位,Spectre 和 Tempus 也有相当的用户。相比较而言,synopsys 的 EDA 工具在数字电路设计的流程中更具有优势,Dc、Pt 和 Formality 具有绝对的市场地位,ICC2 和 Hspice 具有领先的市场地位,VCS 和 DFTCompiler 也被广泛应用。Mentor 的部分点工具则十分出色,比如 Tessent 和 Calibre,这也是非常难能可贵的。

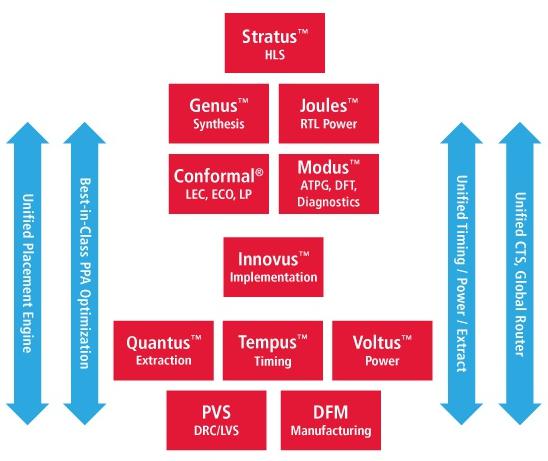

那么每个 IC 设计环节可以用什么 EDA 工具来实现,系列的 EDA 工具(Vendor 称之为全家桶)是如何相互搭配来完成全流程设计的呢?下面以 C 家的工具为例来说明。

图四 C 家数字芯片设计流程对应 EDA 工具

部分名词解释:

HLS : High-level synthesis,高层次综合。

LEC : Logic equivalence check, 逻辑等价性检查。

ECO : Engineer changing order,技术更改指令,可以通过修改 netlist 或者物理实现以修正小的逻辑错误。

DRC : Design rule check,设计规则检查,检查版图是否符合工艺规范。

LVS : Layout versus schematic,一致性检查,保证原理图和版图的一致性。

C 家在前端提供了 Stratus 这款高层次综合平台(HLS,high-level synthesis),Genus 用作综合(synthesis),Joules、Conformal 和 Modus 分别用在功率分析、逻辑等价性检查、逻辑修正及自动测试逻辑插入等。从受欢迎程度来看,C 家的 EDA 工具在数字前端有些弱。

Innovus 作为当家产品则为后端提供强大的布局布线功能,应用于时序和功耗和 Tempus 和 Voltus 也可圈可点,Quantus、PVS 和 DFM 则分别用在寄生参数提取,物理验证和可制造性设计。

由此可见,C 家可以提供数字全流程的全家桶,据悉,有些公司就会直接采购 C 家的全家桶用于 IC 设计,不同工具使用的交互兼容性上会更好一些。而大规模一些的公司,则会选择每个设计环节最主流的 EDA 工具以保证更高的精度和速度,以确定获取更加 golden 的结果。

网友留言: