一、spyglass | 基础操作

SpyGalss是目前业界唯一可靠的RTL Sign off解决方案,可以帮助客户在设计早期发现潜在问题,保证产品质量,极大的减少设计风险,降低设计成本。

包含五大模块:lint, CDC(跨时钟域检查), LP(低功耗),Constraint(约束),DFT(可测试性)。

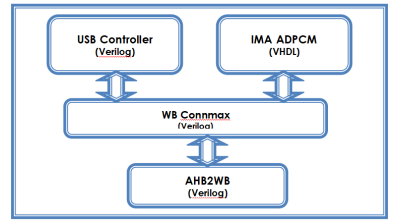

本文测试用例

该测试设计包括具有符合 Wishbone 总线的 USB 控制器 (USB) 和音频解码器内核 (IMA_ADPCM)。这些组件连接到 Wishbone 连接矩阵 (WB_Conmax),后者又使用 Wishbone-to-Amba 桥 (wb2ahb) 连接到 AMBA 总线。该设计属于混合 RTL 类型,同时使用 Verilog 和 VHDL,如下方框图所示:

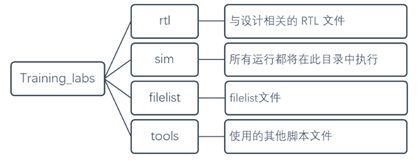

设计目录结构:

包括:rtl(用于存放代码),sim(用于存放中间文件和工程文件)、filelist文件等。

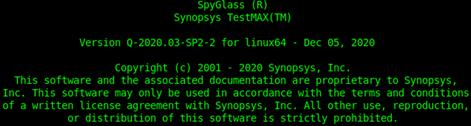

spyglass GUI操作

首先我们在sim目录中打开spyglass GUI界面操作:

读取设计文件

GUI界面打开spyglass

spyglass &

然后点击Add File(s)添加文件:

所需文件路径存放在filelit文件中:

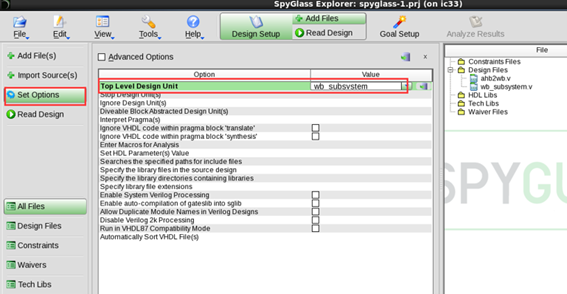

设置顶层模块

添加完文件后点击Set Options,然后选择列表中选择Top Level Design Unit,Value值为顶层模块名,如下图所示:

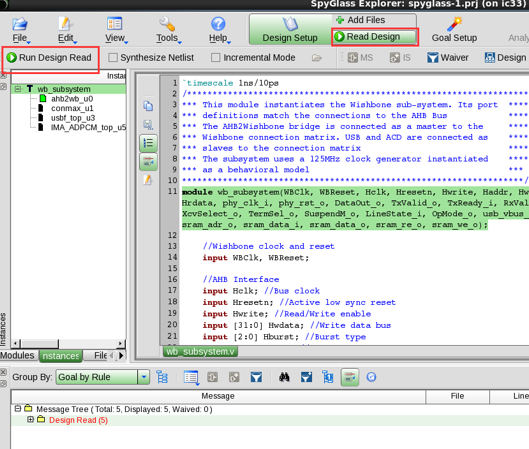

编译设计

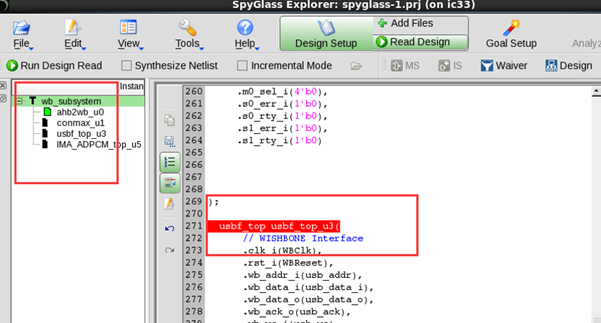

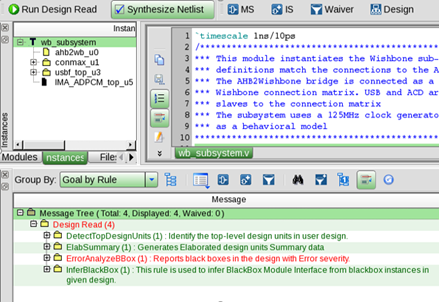

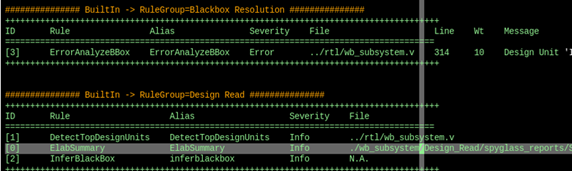

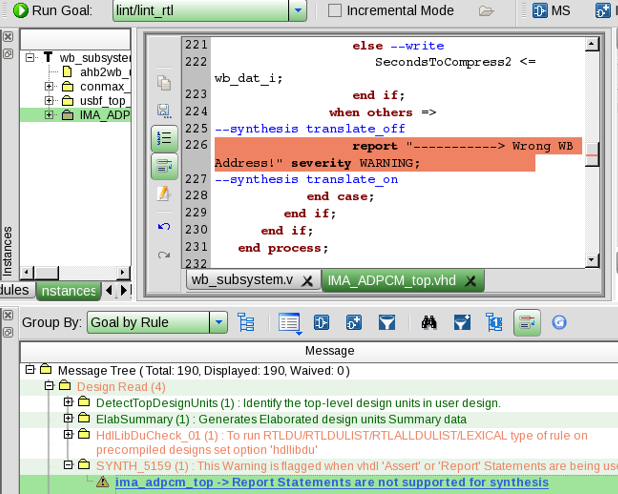

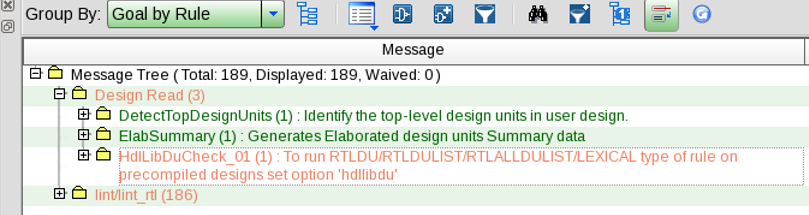

点击Read Design,再在左侧点击Run Design Read开始进行设计文件编译和分析,在读取完成后会在下方窗口列出问题。如下图所示:

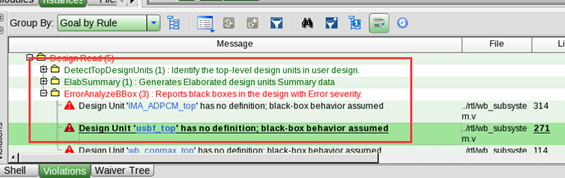

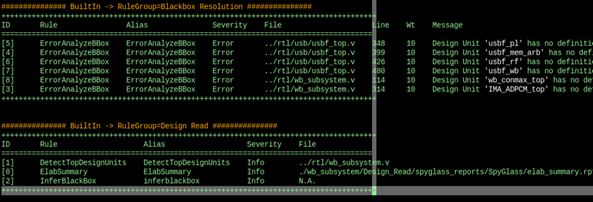

如下图,其中三个问题类型都为ErrorAnalyzeB Box,这是因为有的模块文件没有添加,spygalss无法找到,后面spygalss会将其作为黑盒子处理。

左侧instance下文件不同颜色标识意义为:

•绿色表示已准备好进行分析但尚未在内部综合;

•黑色表示无法分析该块(黑框);

•白色表示该模块是可综合的;

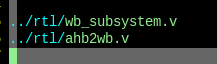

注意:默认情况下,设计读取不合成设计,因此尚未创建原理图。要使用 SpyGlass 进行完整的设计分析,应首先解决所有黑框,并且选择复选框Synthesize Netlist, 并重新运行Run Design Read。因此我们需将设计文件路径全部包括进去,在filelist添加以下文件:

../rtl/usb/usbf_top.v

../rtl/usb/usbf_utmi_if.v

../rtl/usb/usbf_utmi_ls.v并且将conmax、usb等库文件添加进去,重新Run Design Read。如下,ErrorAnalyzeB Box问题已经解决2个,还有一个问题是IMA_ADPCM引起的,后面会解决。

静态分析

下面列出使用spyglass来进行lint分析的步骤。注意使用spyglass进行分析不要求完整的工程文件。

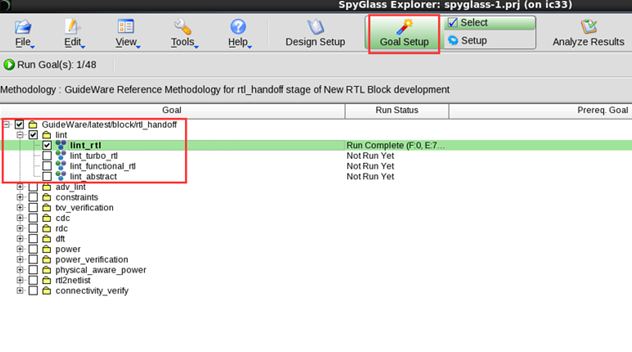

首先选择Linting RTL分析。在窗口上方中间点击Goal Setup ,然后在主窗口区勾选Lint_rtl:

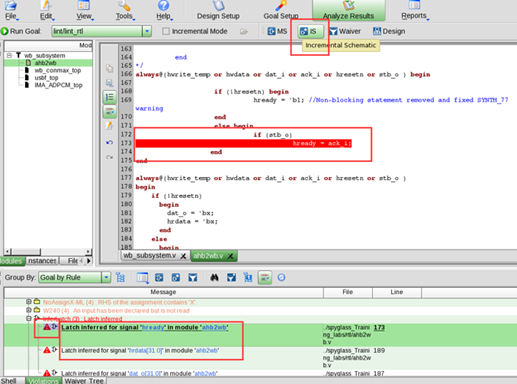

得到结果后,查看Lint分析结果。首先展开lint/lint_rtl文件夹消息。选择并展开inferLatch文件夹,错误相关的代码会在RTL代码窗口中显示出来:

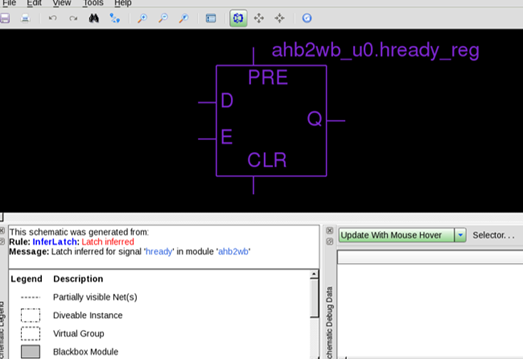

点击 符号得出电路图如图:

符号得出电路图如图:

由电路和.v文件都可得出,这是因为hready信号没有在else后赋值,生成了锁存器。如果这些Latch是故意的,那通过屏蔽对该处的规则检查即可,否则我们修改代码后重新运行Goal。

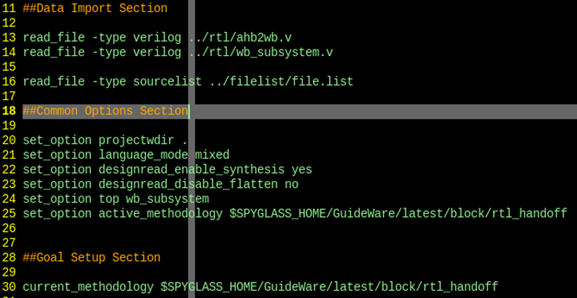

最后save工程后关闭,打开工程文件wb_subsystem.prj,打开的文件如下:

- read_file: 命令定义了在 SpyGlass 运行期间要读取的各种类型的文件。

- language_mode: 选项用于指定当前 SpyGlass 运行的操作语言。默认值为"混合",(将处理 Verilog、VHDL 和混合语言设计)。

- projectwdir: 选项用于指定项目工作目录

- GuideWare/latest : 是默认规则设置,它在项目文件中定义为 active_methodology。

可以在wb_subsystem.prj中,将这些源文件列表添加进去:

read_file -type sourcelist ../filelist/file.list

read_file -type sourcelist ../rtl/wb_conmax/file.listspyglass 命令操作

在上述基础上,将使用-batch选项在批处理模式下运行SpyGlass。同样的操作也可以在GUI模式下完成。

通过下面的指令来运行SpyGlass工程:

spyglass -project wb_subsystem.prj -designread -batch

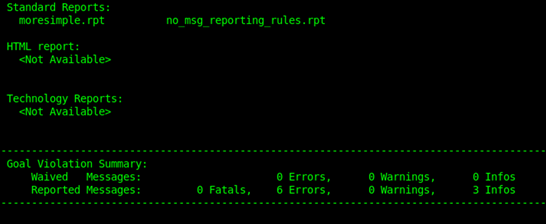

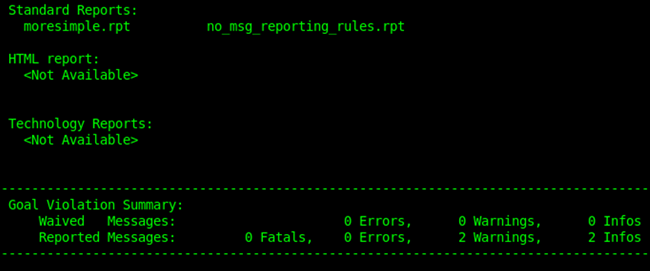

提示有6个错误。SpyGlass会生成比较多的报告,其中常用的报告为:

./wb_subsystem/wb_subsystem/Design_Read/spyglass_reports/moresimple.rpt其内容如下:

它们是被实例化的标准单元,提示没有定义。这些单元很可能会使用 -y/-v 选项传递,所以我们在 usb中的目录,看是否有没有加进去的库文件。可以看到 usb_lib 目录存在于usb目录中,但没有指定 -y 作为 file.list的一部分。

通过在 .prj中添加以下内容,指定Verilog库路径../rtl/usb/usb_lib和库文件扩展名.v以读取缺失的定义:

set_option y { ../rtl/usb/usb_lib }

set_option libext { .v }然后重新执行命令spyglass -project wb_subsystem.prj -designread -batch

可以看到剩下的一个黑盒错误来自IMA_ADPCM_top。这部分采用VHDL设计,出现黑盒问题原因是其设计文件尚未包含在.prj文件。

预编译库来解决IMA_ADPCM_top黑盒问题

预编译HDL库,需要指定逻辑库中要预编译的文件列表,以及逻辑库名和物理目录的映射关系。这是使用lib_hdlfiles(定义要编译到命名库的文件)和 lib(将命名库映射到物理目录)选项来完成的:

set_option libhdlfiles ima_adpcm_lib "../rtl/ima_adpcm/IMA_ADPCM_Encode.vhd \

../rtl/ima_adpcm/IMA_adpcm_steptable_rom.vhd \

../rtl/ima_adpcm/WAV_header_rom.vhd \

../rtl/ima_adpcm/IMA_ADPCM_top.vhd "

set_option lib ima_adpcm_lib ../ima_adpcm_lib首先删除包含上次运行保存的网表的结果目录,然后重新运行,确认这个最新的项目文件解决了来自IMA_ADPCM_top的黑盒错误:

rm -rf wb_subsystem

spyglass -project wb_subsystem.prj -designread –batch

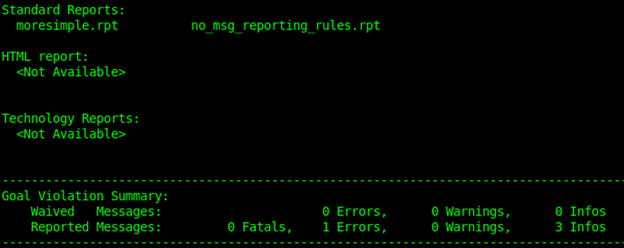

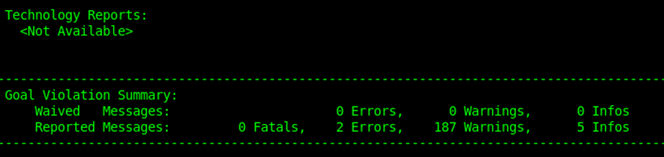

运行Goal及查看报告信息

通过下面命令来获取可用的Goal列表:

spyglass –project wb_subsystem.prj -showgoals

使用如下命令来运行lint/lint_rtl分析:

spyglass -project wb_subsystem.prj -goals lint/lint_rtl -batch

在文件

./wb_subsystem/wb_subsystem/lint/lint_rtl/spyglass_reports/moresimple.rpt

中查看更为详细的报告:

二、spyglass | 常见错误lint

我们将分析 lint目标运行期间产生的违规行为。我们可以使用 SpyGlass GUI 中的各种调试工具来了解违规,在 RTL 代码中调试,并查看如何在 SpyGlass 环境本身中修复这些违规。并且在更改 RTL或者.prj文件之后都必须重新运行。

使用以下命令打开 SpyGlass GUI,将自动加载上次运行目标 (lint/lint_rtl)

spyglass -project wb_subsystem.prj &

在没有-batch时,SpyGlass 默认会打开 GUI。

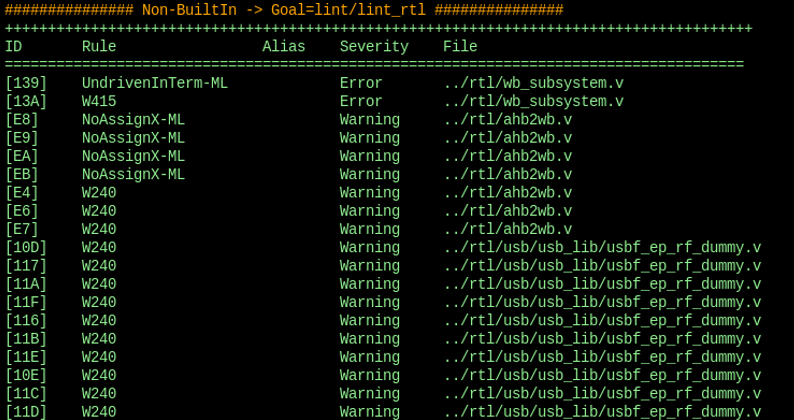

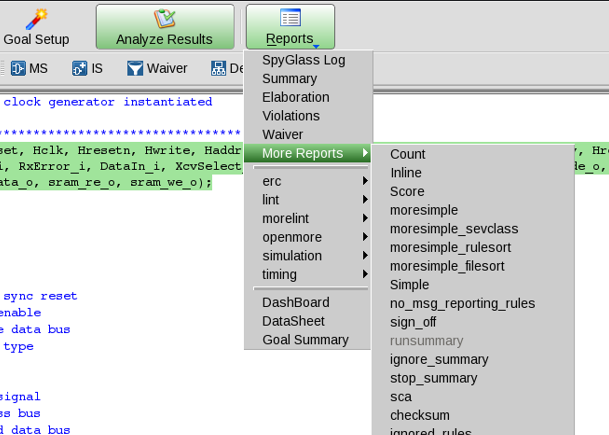

生成对应于每个目标运行的多个报告,可从菜单栏的报告部分访问,如下所示:

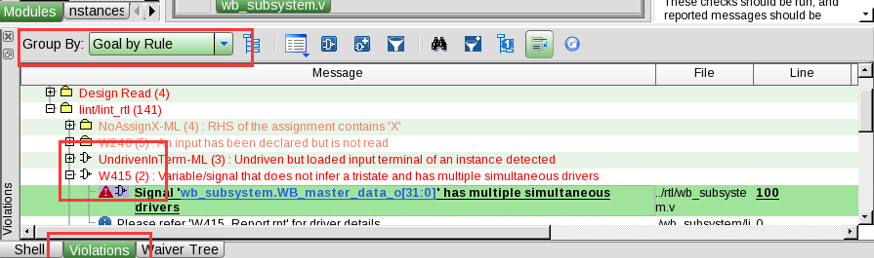

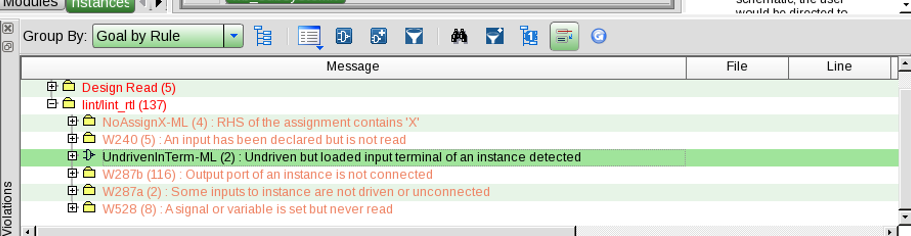

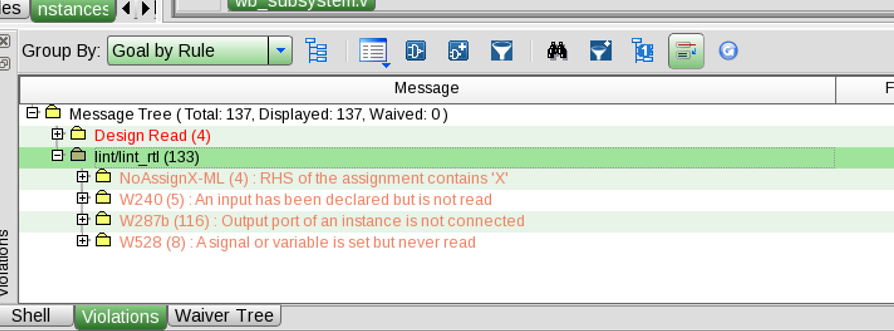

在GUI底部的Violations可查看违规信息。在显示出违规信息后,点击违规信息窗口顶部的Group By,然后选择Goal by Rule。

W415 Multiple drivers错误

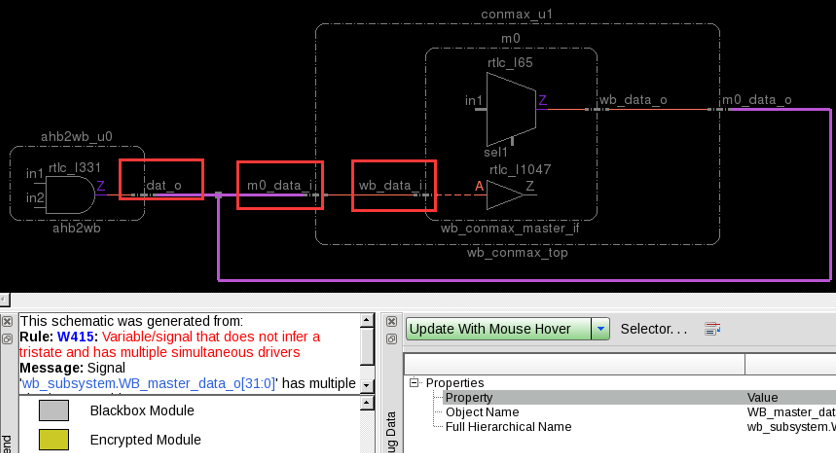

该规则确定了可以由设计中的 2 个或更多非三态驱动器同时驱动的网络。打开原理图窗口,增量示意图窗口显示违规的结构:

可以看到两个驱动程序正在驱动信号 (WB_master_data_o[0]) ,即端口m0_data_i由端口dat_o(例如 ahb2wb_u0)和m0_data_o(例如 conmax_u1)同时驱动。因此,这是一个违规行为。

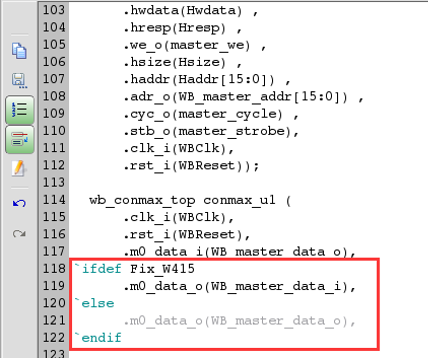

通过查看RTL代码知道该部分使用ifdef构造来启用固定代码。

因此在wb_subsystem.prj中添加以下内容来启用宏,从而启用Fix_W415宏:

set_option define { Fix_W415 }设置后重新加载项目文件和重新运行spyglass -project wb_subsystem.prj &

SYNTH_5159警告

规则 SYNTH_5159识别可能无法综合的结构。该语句包含在synthesis编译指示中,表明该语句不用于分析,但默认情况下,SpyGlass 仅将synopsys和pragma注释识别为pragma(编译指示)(与 Design Compiler 相同)。我们需要通过在.prj文件中添加以下内容来启用synthesis的pragma处理:

set_option pragma { synopsys pragam synthesis}由于此错误发生在ima_adpcm_lib预编译库中,SpyGlass会检查该库的RTL是否已更改,只有在更改后才会重新编译,因此我们需要删除现有的预编译库,使用新的pragma设置重新编译该库。

rm -rf ima_adpcm_lib

重新运行后,SYNTH_5159警告消除。

注意: 手动删除 ima_adpcm_lib的替代方法是在.prj文件中临时添加set_option force_compile yes以强制重新编译库。

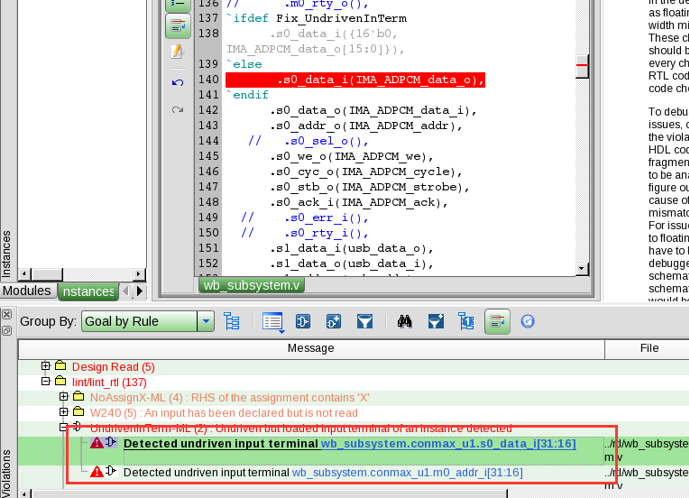

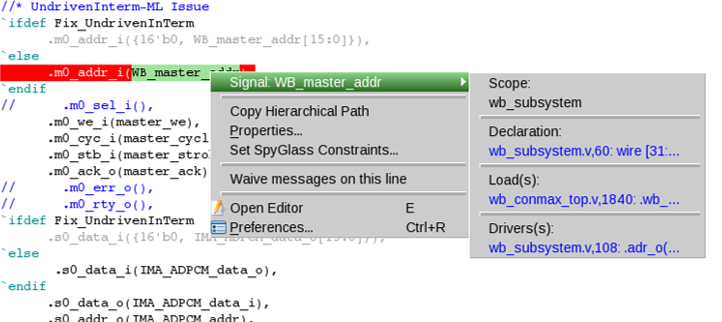

UndrivenInTerm-ML错误

查看违规消息,发现"conmax_u1"矢量输入端口"m0_addr_i"的上半部分(31:16)范围被发现是浮动的:

- 首先双击违规消息, RTL 代码中突出显示的行显示了矢量端口m0_addr_i的端口映射,该端口映射与矢量信号WB_master_addr。

- 在RTL显示行上,选择WB_master_addr信号(双击),从右键菜单窗口中选择选项Signal:WB_master_addr:

折叠菜单显示了声明、加载和驱动程序的许多超链接(蓝色字样)。可以看到向量信号WB_master_addr的宽度为32位,与映射的实际端口m0_addr_i的宽度相同,即端口与相同大小的信号总线完全连接,不是问题所在。

因此我们继续检查向量信号WB_master_addr的驱动程序:

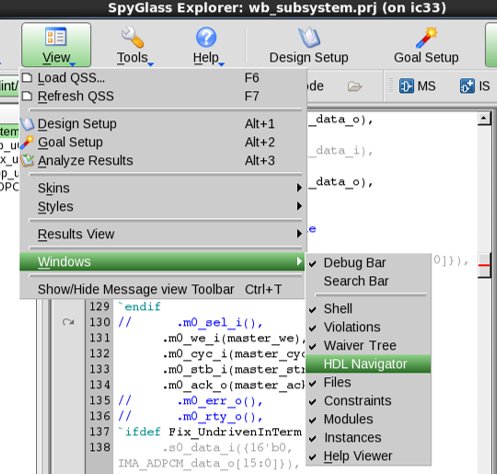

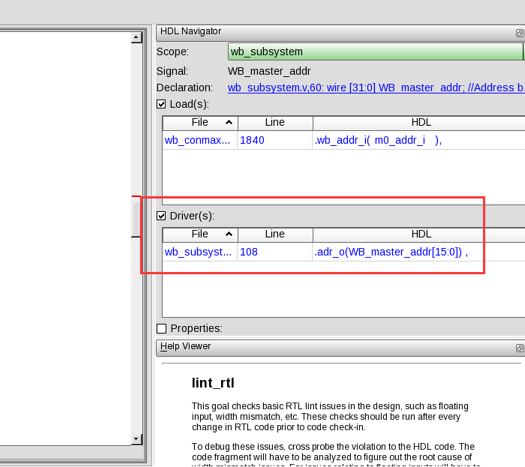

使用 View -> Windows -> HDL Navigator打开 HDL Navigator窗口,这显示了所选WB_master_addr的驱动器和负载。

注意到存在一个 RTL 驱动程序信息:

驱动程序是实例ahb2wb_u0的o/p端口adr_0,但这仅驱动矢量信号WB_master_addr的低位(15:0),其余位没有报告其他驱动程序 WB_master_addr ,即高位没有驱动程序。此违规的修复方法是将高 16 位赋值为0,并需要更新 RTL。

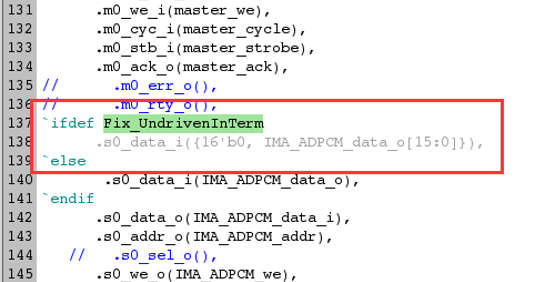

可以看到RTL中有通过拼接进行的驱动程序,但通过ifdef结构进行控制。因此可以通过设置Fix_UndrivenInTerm宏来调用目标程序:

set_option define { Fix_UndrivenInTerm }

通常,用户不希望每次运行 SpyGlass 时都看到违规消息。可以通过定义Waive来过滤它们 。

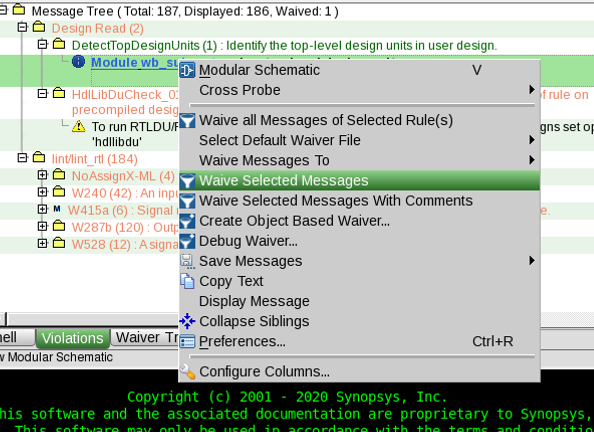

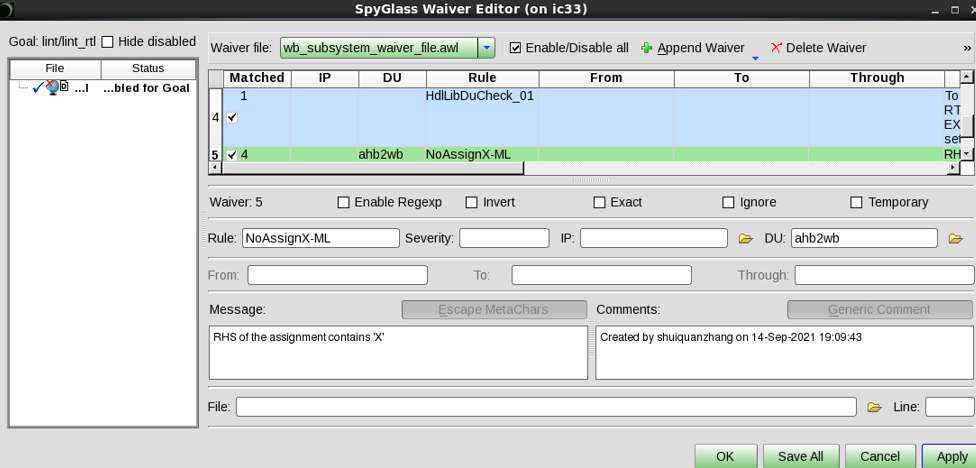

右键单击Waive Selected Messages这将打开Waive编辑器窗口,并为其填充相关信息(违规消息、规则和设计单元 (DU))

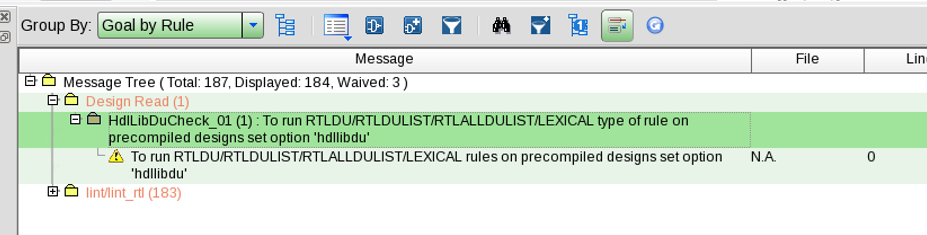

单击Apply,如下图,已忽略刚刚的警告信息。

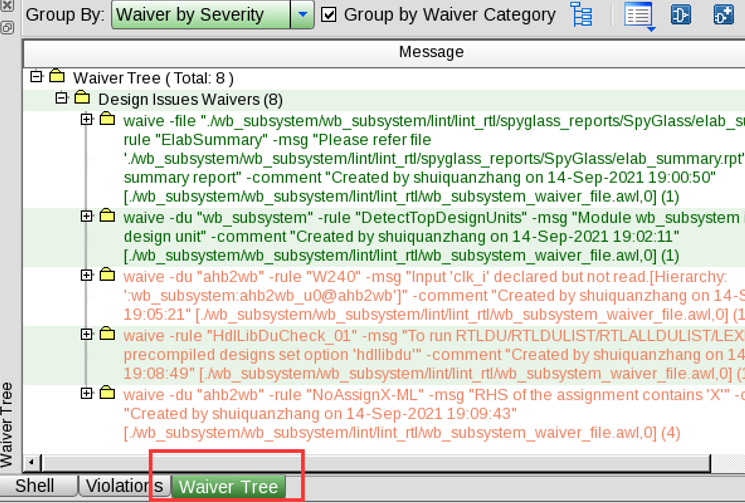

在界面底部选择Waiver Tree可以查看已经被过过滤掉的错误选项。

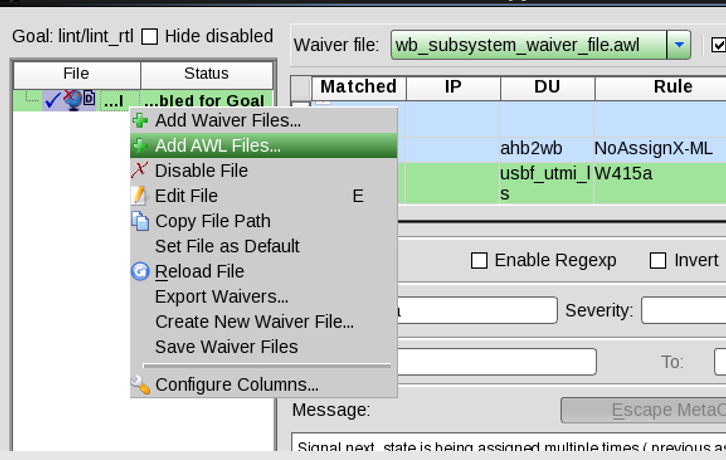

如果想在后续继续使用当前生成的Waiver,可以将这些信息保存在一个Waiver文件 (.awl) 中。在waivers编辑器窗口中右键文件,然后选择选项Save Waiver Files。:

SpyGlass会为每个Goal保存一个关于检查过滤的文件,本例中文件路径为:

./wb_subsystem/wb_subsystem/lint/lint_rtl/wb_subsystem_waiver_file.awl

我们可以将其复制到当前工作目录下,方便调用:

cp ./wb_subsystem/wb_subsystem/lint/lint_rtl/wb_subsystem_waiver_file.awl ./wb_subsystem.awl

然后将该过滤文件包含到工程中并将其设置为默认waiver 文件:

read_file -type awl ./wb_subsystem.awl

set_option default_waiver_file ./wb_subsystem.awl然后重新加载工程文件且运行Goal。

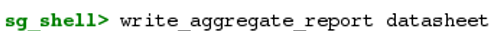

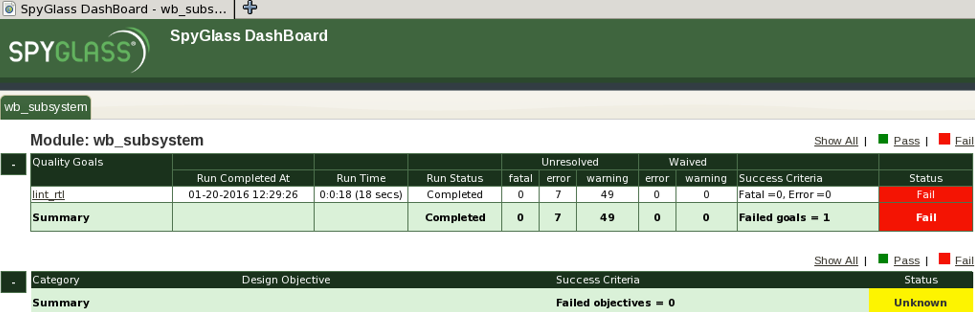

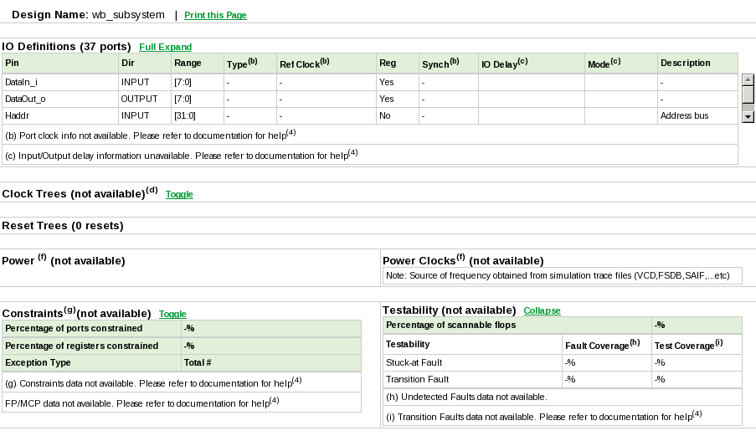

生成Dashboard/Datasheet

在GUI界面下打开shell命令窗口,输入如下命令生成Dashboard/Datasheet:

write_aggregate_report datasheet

write_aggregate_report dashboard

通过在终端中输入下面命令可以在浏览器中查看报告

firefox wb_subsystem/html_reports/dashboard.html

firefox wb_subsystem/html_reports/datasheet.html

最后可以查看.prj文件:

参考网页:

https://cloud.tencent.com/developer/article/1887323 https://www.zhihu.com/column/c_1252190743608815616

文章来源自网络,如有侵权,请随时联系我们

网友留言: